How to tackle setup violations in timing analysis?

How to tackle setup violations: The ultimate goal of timing analysis is to get every timing path follow setup equation and get a positive setup slack number for every timing path in the design.

What to do if a timing path is violating setup timing?

If a timing path is violating setup timing (assuming we are targetting a certain clock frequency), we can try one or more of the following to bring the setup slack back to a positive value by: How to fix setup violations discusses various ways to tackle setup violations.

What is timing and why is it so important?

A choice of utmost importance refers to the relative timing of a few key events that repeat in every stimulus/response cycle. Poor timing may cause a gate-level model to report hundreds of hold time violations per clock cycle during a simulation run, for instance, whereas a purely algorithmic model is simply not concerned with physical time.

What does no timing violation mean in a flip flop?

In other words, no timing violations means that the data launched by one flip-flop at one clock edge is getting captured by another flip-flop at the desired clock edge. If the setup check is violated, data will not be captured properly at the next clock edge.

How can I fix my time violation?

Since setup time violation can be solved by decreasing the data path logic delay, using a flop with a smaller clock-q delay for launch flip-flop will ease timing requirement. Using a faster cell for launch flip-flop: Flip-flop comes with various threshold voltage (VT).

Which of the following can cause timing violations?

Violations can be caused by routing paths that are too long, insufficient constraint definitions, clock skew, and a number of other causes.

What are timing violations in VLSI?

If M > Tclk – S , it results into timing violation, called as Setup violation. This means, that the combinational logic delay is very large and hence data change is very slow. To satisfy the 'setup' requirement, the combinational logic delay should be decreased.

What happens if setup time is violated?

Any violation may cause incorrect data to be captured, which is known as setup violation. Hold time is defined as the minimum amount of time after the clock's active edge during which data must be stable. Violation in this case may cause incorrect data to be latched, which is known as a hold violation.

Which of the following are the plausible reasons for the hold time violations?

Hold violation happen when data is too fast compared to the clock speed. For fixing the hold violation, delay should be increases in the data path.

How do you fix the hold time violation after the chip was fabricated?

There is no way to fix setup or hold violation after fabrication. One thing generally industry does is to sell the chip at lower operating frequency if there is setup violation. If there is a hold violation, chip will be thrown into garbage.

How do I fix a VLSI transition violation?

Fixing Transition ViolationUp sizing the driver cell.Decreasing the net length by moving cells nearer or reducing long routed net.By adding buffers.By using existing spare cells as buffers.By splitting loads through buffers to reduce the fan out number (number of driven cells)

What is Crosstalk in VLSI?

Crosstalk is a phenomenon, by which a logic transmitted in vlsi circuit or a net/wire creates undesired effect on the neighbouring circuit or nets/wires, due to capacitive coupling. Refer to the digram below to get a clear picture on the effect of coupling capacitance on functionality and timing of VLSI circuits.

How do I fix a static IR drop in VLSI?

How to reduce the IR Drop-in VLSI?Use proper width of Metal according to current density.Use more parallel metal wire strips.Spread the logic if hotspots are in congested areas.Add more proper vias.Use proper CTS structure.Add buffers if the run length of the wire is too long.Avoid the jogs in metals.More items...

Which is hard to fix setup violation or hold violation and why?

hold violation is more dangerous than setup voilation . Becuase after timing clourse also we can adjust the freqency . so by that we can aviod setup voil . but hold violation is not dependent on freqency.

What causes setup and hold time?

Setup time is the amount of time required for the input to a Flip-Flop to be stable before a clock edge. Hold time is similar to setup time, but it deals with events after a clock edge occurs. Hold time is the minimum amount of time required for the input to a Flip-Flop to be stable after a clock edge.

What is a setup time?

What is Setup Time? Setup time is the interval needed to adjust the settings on a machine, so that it is ready to process a job. Shortening the amount of setup time is critical for engaging in short production runs, so that a business can more easily engage in just-in-time production.

What are DRV violations?

DRV(Design Rule Violations) and DRC(Design rule check) are the terms used judge the quality of chip in different stages in VLSI Physical Design. DRC: It is actually used for making sure layout of a design must be in accordance with a set of predefined technology rules given by the foundry for manufacturability.

What is timing analysis in VLSI?

Static timing analysis (STA) is a way of evaluating a design's timing performance by testing for timing violations along all conceivable paths. Dynamic simulation, which determines the whole behaviour of the circuit for a given set of input stimulus vectors, is another technique to do timing analysis.

How do you fix a max transition violation in VLSI?

How to fix max trans violation? Increase the driver size. Break the nets in the case of long nets. Break the large fanout by duplicating drivers or with buffering. Change the VT if option available(changing drivers from hvt to svt or lvt).More items...•

What are sanity checks in VLSI?

Sanity checks are an important step for physical design engineers to make sure that the inputs received for physical design are correct and consistent. Any issues in the input files may cause problems in the later stages.

Finding Slack and Violations

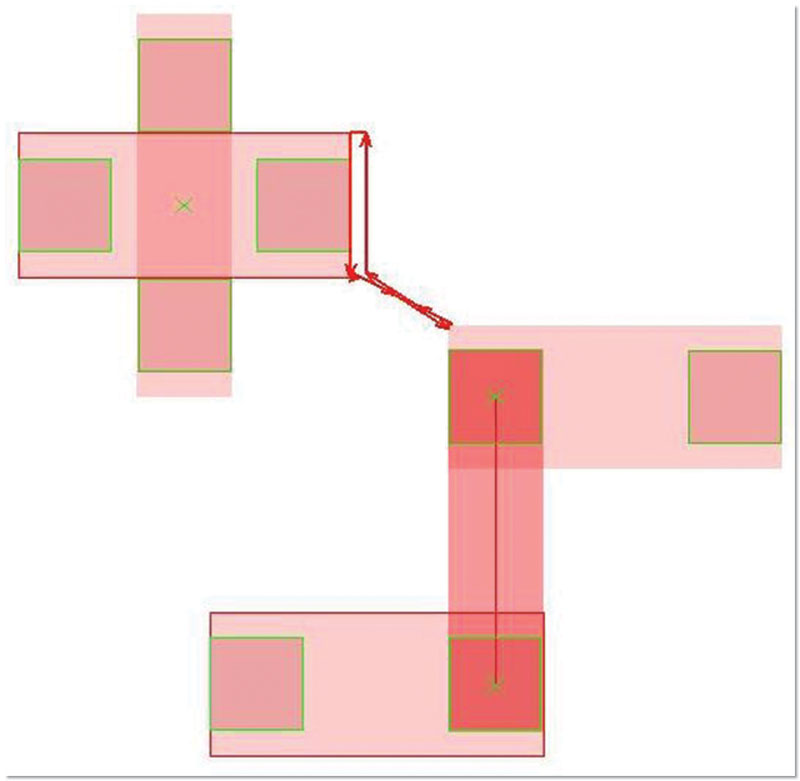

In the applet below, you can control the source and destination register clock buffer delays with your pointer (mouse/finger).

Timing Analysis

Without clock skew, a setup time and hold time violation checks are simple.

Questions

How does increasing the destination register clock delay affect setup and hold slack?

Why is min delay a problem?

Min-delay is a serious problem because unlike setup time violations, hold time violations cannot be fixed by adjusting the clock frequency. Instead, the designer must conservatively guarantee adequate delay through logic between clocked elements. Min-delay problems should be checked at the interfaces listed in Table 4.4. The top half of the table lists common cases encountered in typical designs. The bottom half of the table lists combinations, which while technically legal according to Table 4.2, would not occur in normal use because ϕ 2 and ϕ 4 transparent latches and N-latches are seldom used.

How to solve min delay?

Min-delay problems can be solved in two ways. One approach is to add explicit delay to the data. For example, a buffer made from two long-channel inverters is a popular delay element. Another is to add a latch between the elements controlled by an intervening phase. Both approaches prevent races by slowing the data until the hold time of the second element is satisfied. Examples of these solutions are shown in Figure 4.19. In path (a) there is no logic between latches. If ϕ 1 and ϕ 3 are skewed as shown, data may depart the ϕ 1 latch when it becomes transparent, then race through the ϕ 3 latch before it becomes opaque. Path (b) solves this problem by adding logic delay δ logic, as was discussed in Section 2.2.4. Path (c) solves the problem by adding a ϕ 2 latch. If the minimum required delay is large, the latch may occupy less area than a string of delay elements.

Is sequencing overhead a problem?

In this chapter we have examined the sources of sequencing overhead and seen that it is a growing problem in high-speed digital circuits, as summarized in Table 1.3. While flip-flops and traditional domino circuits have severe overhead, transparent latches and skew-tolerant domino circuits hide clock skew and allow time borrowing to balance logic between pipeline stages. In the subsequent chapters we will flush out these ideas to present a complete methodology for skew-tolerant circuit design of static and dynamic circuits.

How to analyze timing?

When performing timing analysis, STA first breaks down the design into timing paths. Each timing path consists of the following elements: 1 Startpoint. The start of a timing path where data is launched by a clock edge or where the data must be available at a specific time. Every startpoint must be either an input port or a register clock pin. 2 Combinational logic network. Elements that have no memory or internal state. Combinational logic can contain AND, OR, XOR, and inverter elements, but cannot contain flip-flops, latches, registers, or RAM. 3 Endpoint. The end of a timing path where data is captured by a clock edge or where the data must be available at a specific time. Every endpoint must be either a register data input pin or an output port.

What is a hold violation in STA?

A hold violation can occur if the clock path has a long delay. If certain paths are not intended to operate according to the default setup and hold behavior assumed by the STA tool, you need to specify those paths as timing exceptions. Otherwise, the tool might incorrectly report those paths as having timing violations.

What is an endpoint in a timing path?

Endpoint. The end of a timing path where data is captured by a clock edge or where the data must be available at a specific time. Every endpoint must be either a register data input pin or an output port.

Why is static timing analysis faster than dynamic simulation?

Compared to dynamic simulation, static timing analysis is much faster because it is not necessary to simulate the logical operation of the circuit. STA is also more thorough because it checks all timing paths, not just the logical conditions that are sensitized by a set of test vectors. However, STA can only check the timing, not the functionality, ...

What is cell delay?

Cell delay is the amount of delay from input to output of a logic gate in a path. In the absence of back-annotated delay information from an SDF file, the tool calculates the cell delay from delay tables provided in the logic library for the cell.

What is delay table?

Typically, a delay table lists the amount of delay as a function of one or more variables, such as input transition time and output load capacitance. From these table entries, the tool calculates each cell delay.

What is static timing analysis?

Static Timing Analysis (STA) is one of the techniques to verify design in terms of timing. This kind of analysis doesn’t depend on any data or logic inputs, applied at the input pins. The input to an STA tool is the routed netlist, clock definitions (or clock frequency) and external environment definitions. The STA will validate whether the design could operate at the rated clock frequency, without any timing violations. Some of the basic timing violations are setup violation and hold violation

What factors affect the delay of a gate?

This delay will not be fixed as the effective load capacitance seen by each gate in the design is different. Other factors that affect the delay of a gate such as input transition, threshold voltage, drive strength, etc.

How many timing paths does a NAND gate have?

The above example illustrates for 2-input NAND gate, it has two timing paths.More complex logic gates will have even more timing paths, e.g. 10 input MUX. Thus, the delay between Sender and Receiver is not constant, but will have range of values, as shown below.

Does data change between hold time H and M?

The data is not expected to change between hold time ‘H’ to ‘m’ and ‘M’ to (T clk – Setup time ‘S’). Data changes somewhere between ‘m’ and ‘M’, and becomes stable after that.

What is setup and hold violations?

What is meant by setup and/or hold violations: The ultimate aim of timing analysis is to get the design work at required frequency and with reliability. For this to happen, it must be ensured in timing that all the state transitions are happening smoothly; i.e., the setup and hold requirements of all the timing paths in the design are met. If there are failing setup and/or hold paths, the design is said to have violations.

What happens if you violate setup and hold?

If the setup check is violated, data will not be captured properly at the next clock edge. Similarly, if hold check is violated, data intended to get captured at the next edge will get captured at the same edge. Moreover, setup/hold violations can lead to data getting captured within the setup/hold window which can lead to metastability of the capturing flip-flop (as explained in our post metastability ). So, it is very important to have setup and hold requirements met for all the registers in the design and there should not be any setup/hold violations.

Why is timing important in mutual funds?

Mutual fund timing is legal and can help investors to profit from trading opportunities or trades enacted at opportune times of market changes. However, mutual fund timing is often discouraged by mutual fund companies because of the negative affects it has on a fund.

What Is Mutual Fund Timing?

Mutual fund timing is a legal but often discouraged practice whereby traders attempt to profit from short-term differences between the price of mutual funds and the individual securities in those funds. This is possible because mutual fund prices only change once per day.

When was mutual fund timing investigated?

Regulation and Investigations. Mutual fund timing is closely monitored by both regulators and fund companies. In September of 2003, some mutual fund companies were investigated for permitting traders to "time" mutual fund purchases.

Is the practice of redemption of shares detrimental to long term investors?

The practice is detrimental to long-term investors since the additional redemptions of shares by short-term profiteers generates excess fund management costs.

Is market timing legal?

With these techniques, market timing can be legal when transacted appropriately. It can also generate profits even after redemption fees. In the case of closed-end funds and exchange-traded funds (ETFs), market opportunities may be easier to identify.

Is market timing a good investment?

Profit Opportunity. Overall, when legally transacted, market timing can be a profitable way to add value. Just as with stocks , mutual funds may have opportunities for short-term gains that make trading beneficial for profit.

Is Mutual Fund Timing Illegal?

Mutual fund timing is not illegal by itself unless it violates other securities laws or investor protections. For example, many mutual funds have rules to discourage fund timing listed in their prospectus, with additional costs or barriers to short-term traders. A fund manager who selectively allows some traders to break those rules could be breaking the law. Likewise, if a mutual fund or brokerage bars someone for trading too frequently, it is illegal for that person to use deceptive means to continue trading.